在数据采集系统中,ADC是连接模拟信号与数字信号的核心部件,其转换精度直接决定系统性能。增益误差作为ADC的关键静态误差指标之一,会导致实际输出与理想输出的比例偏离,严重影响信号采集的准确性。

本文将从增益误差的详细定义与量化公式入手,系统分析芯片自身及PCB板级的误差来源,并针对性提出从选型到设计的完整解决方案。同时,结合德思特 ADC/DAC 测试系统的高性能特性,阐述其在 ADC 增益误差精准评估中的核心价值。

一、增益误差的核心定义与量化公式

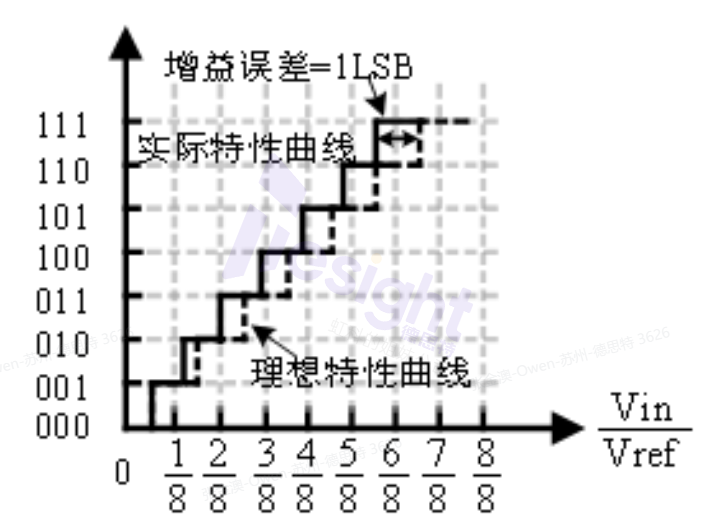

要精准控制增益误差,首先需明确其本质内涵与量化方法。增益误差的核心是ADC在 linear 工作范围内,实际转换增益与理想转换增益的偏差,反映了器件对输入信号放大/缩小能力的偏离程度。

1.详细定义

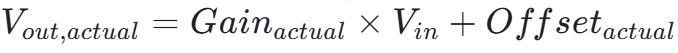

• 理想ADC的转换关系遵循线性方程:

其中,Gain_{ideal} 为理想增益(通常为固定值,如单端输入时为数字满量程与模拟满量程的比值),Offset_{ideal} 为理想失调误差(仅关注增益特性时可默认忽略)。

• 实际ADC因器件特性限制,转换关系为:

其中,Gain_{actual}为实际增益,Offset_{actual}为实际失调误差。需特别注意的是,计算增益误差时需先消除失调误差的影响(或在满量程输入下计算,此时失调误差占比可忽略),否则会将失调误差误计入增益误差。

简单来说,当输入信号达到ADC的满量程值V_{in,FS} 时,实际输出与理想输出的偏差本质就是增益误差导致的。

• 例如:12位ADC的模拟满量程V_{in,FS}=5V,理想数字满量程V_{out,ideal,FS}=4095,理想增益Gain_{ideal}=4095/5=819(Code/V);

若实际输入5V时输出仅为4000,实际增益Gain_{actual}=4000/5=800,此时便存在明显的增益误差。

2

核心计算公式

增益误差有三种常用量化形式,可根据实际应用场景(如精度评估、系统校准)选择,均以满量程参数为核心基准。

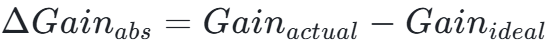

• 绝对增益误差(ΔGain_abs):

直接反映实际增益与理想增益的绝对差值,单位为无单位(因增益是电压/Code的比值)。

公式

推导:

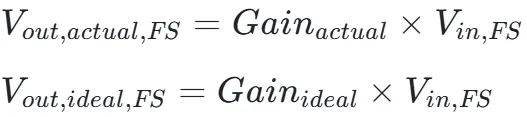

由

可推出

代入后得:

示例:沿用上述12位ADC案例

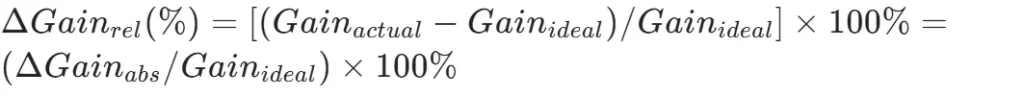

• 相对增益误差(ΔGain_rel):

最常用的量化形式,以理想增益为基准,用百分比表示偏差程度,直观反映误差占比,工业界常标注为“%FS”(满量程百分比)。

公式1(基于增益比):

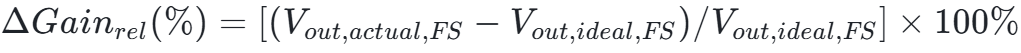

公式2(基于满量程输出):

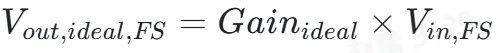

两公式等价,因

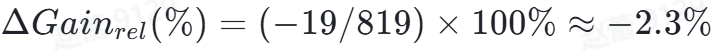

示例:上述案例中,

结果完全一致。

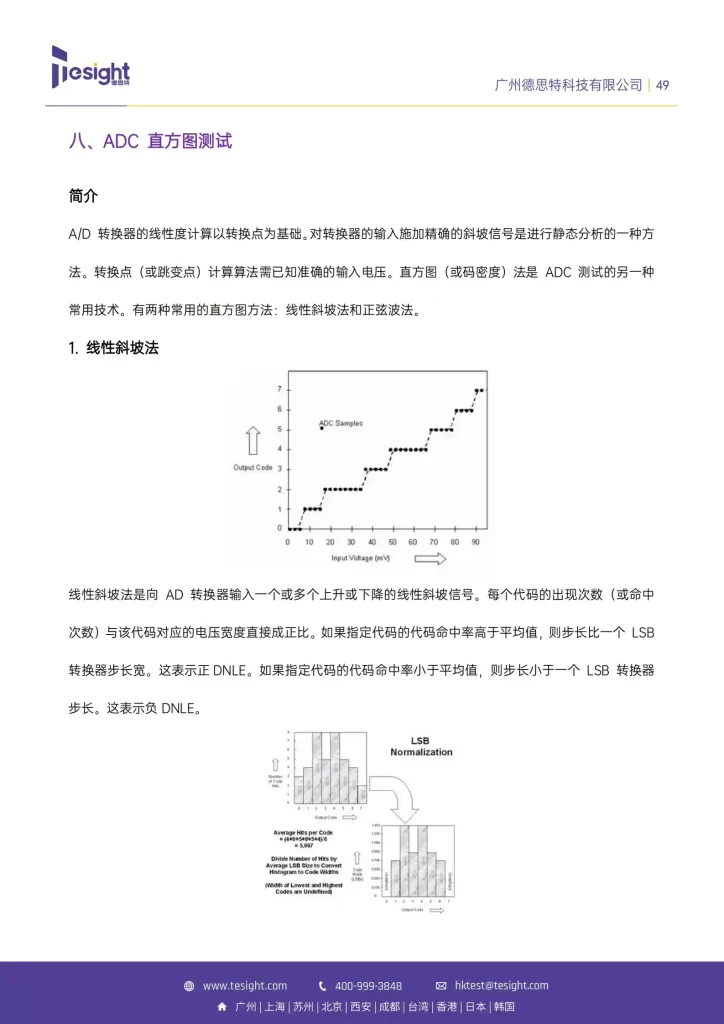

• LSB形式的增益误差:

将误差转换为ADC的最小量化单位(LSB),方便与数字输出精度对齐,常用于数字系统校准场景。

先计算1LSB的电压值:

(N为ADC位数,单端输入)。

公式:

示例:12位ADC(N=12),

则

(数字量差值可直接对应LSB数,因数字量的1LSB对应电压的1LSB)。

二、增益误差的核心来源:芯片自身 vs PCB板级

增益误差的产生源于两方面:一是ADC芯片自身的固有特性,二是PCB设计不当引入的外部干扰。前者无法通过设计完全消除,只能通过选型规避;后者是实际应用中的主要痛点,可通过优化设计有效抑制。

1.芯片自身的固有误差来源

芯片内部设计和制造过程决定了基础误差,是增益误差的“本底来源”。

• 制造工艺偏差:

内部校准电阻、电容的精度有限(如常规精度为±5%),导致内部放大器的增益偏离设计值,这是出厂时就存在的固有误差,无法通过外部设计消除。

• 温度漂移:

温度变化会改变半导体元件的核心参数(如电阻值、运放增益),例如普通ADC温度每升高10℃,增益误差可能增加0.1%FS,高温环境下该误差会进一步放大。

• 电源电压敏感性:

芯片供电电压(如VDD)的波动会影响内部放大器的工作点,例如VDD从3.3V降至3.0V时,部分ADC的增益可能下降1%-2%,电源稳定性直接影响增益精度。

• 内部参考电压(VREF)误差:

若ADC依赖内部VREF,其精度(如常规为±2%)会直接导致增益误差——VREF实际值偏低时,相同输入对应的输出会偏小,等效增益降低;VREF波动则会导致增益不稳定。

2

PCB板级的外部误差来源

PCB设计不当会引入额外误差,甚至掩盖芯片自身的高精度优势,是实际工程中需重点解决的问题。

• 电源噪声耦合:

PCB上数字电路(如MCU时钟、FPGA)或功率电路(如电机驱动、DC-DC转换器)的开关噪声,会通过电源总线耦合到ADC的VDD引脚,干扰内部放大器的稳定性,导致增益波动(通常为±0.5%FS)。

• 参考电压(VREF)布线缺陷:

VREF走线过长、线径过细,或与噪声线(如时钟线、功率线)平行布线,会引入串扰噪声(通常为10-100mV);未在VREF引脚旁加滤波电容时,噪声会进一步放大,间接导致增益误差。

• 信号路径阻抗问题:

ADC输入信号走线过长、线径过细(导致阻抗增大),或与接地平面接触不良,会产生电压压降(I×R),导致实际输入ADC的电压低于真实值,等效增益降低;走线过孔过多也会增加信号损耗。

• 接地不良与地环路:

ADC的模拟地(AGND)与数字地(DGND)未采用单点连接,或接地平面存在分割,会形成地环路,引入共模噪声(如50Hz工频干扰),干扰增益的稳定计算。

• 电磁干扰(EMI):

PCB上的高频信号(如射频模块、高速时钟)会通过空间辐射或走线耦合到ADC输入线,使输入信号叠加噪声,导致增益计算偏差;外部电磁环境也可能通过PCB辐射引入干扰。

三、增益误差的解决方案:从芯片选型到PCB设计

控制增益误差需采用“源头规避+外部优化”的组合策略:通过芯片选型降低固有误差,通过PCB设计消除外部干扰,两者结合可最大限度提升ADC的转换精度。

1.芯片选型:从源头控制固有误差

选择合适的ADC型号是控制增益误差的基础,需重点关注以下核心指标:

• 优先选择出厂校准型ADC:选择带有激光校准或动态自校准功能的型号(如TI ADS1248、ADI AD7799),这类ADC的固有增益误差可低至±0.01%FS,大幅降低后续设计压力。

• 关注温度系数指标:工业级或高温场景下,需选择低温度系数的ADC(如温度系数<2ppm/℃),避免温度变化导致增益漂移;必要时可搭配温度补偿电路。

• 外置高精度参考电压:若ADC内部VREF精度不足(如±2%),建议搭配外置基准芯片(如TI REF5050,精度±0.02%;ADI ADR4550,精度±0.005%),为ADC提供稳定的VREF,从根源消除参考电压带来的增益误差。

• 选择高电源抑制比(PSRR)的ADC:PSRR越高(如80dB以上),ADC对电源电压波动的抗干扰能力越强,电源噪声对增益的影响越小;例如TI ADS1115的PSRR可达86dB@50Hz,适合电源环境复杂的场景。

2.PCB设计:消除外部误差干扰

针对PCB板级的误差来源,需从电源、布线、接地、EMI防护四个维度进行优化设计:

• 电源处理:独立供电+多级滤波:

电源噪声是增益波动的主要诱因,需实现ADC电源的“隔离+净化”:

1. 采用低压差稳压器(LDO,如TI TPS799、ADI ADP125)为ADC单独供电,与数字电路、功率电路的电源完全隔离,避免不同电路的电源噪声相互耦合。

2. 在ADC的VDD和AGND引脚旁,紧贴芯片并联100nF陶瓷电容(滤除高频噪声)和1μF钽电容(滤除低频噪声),电容需尽量靠近引脚(距离<3mm),确保电源噪声幅值<10mV。

3. 若PCB存在强噪声源(如DC-DC转换器),需在LDO输入端额外串联磁珠(如100Ω@100MHz),进一步抑制高频噪声。

• 参考电压:短路径+低噪声布线:

VREF的稳定性直接决定增益精度,布线需遵循“短、粗、远离噪声”原则:

1.VREF走线尽量短(长度<5cm)、线径加粗(≥0.2mm),减少走线阻抗;与时钟线、功率线的间距需>2mm,避免串扰。

2.在VREF输入引脚旁并联10nF陶瓷电容,进一步滤除串扰噪声;若使用外置基准芯片,基准芯片需靠近ADC放置,减少VREF传输损耗。

• 信号路径:低阻抗+抗干扰设计:

输入信号的完整性直接影响增益计算,需优化信号路径:

1.ADC输入信号走线需短而直,线径≥0.2mm,避免使用过孔(过孔会增加阻抗);若信号源与ADC距离较远,建议使用差分信号输入(如ADC支持差分输入),提升抗干扰能力。

2.输入线采用“地线包裹”设计(周围铺AGND),形成屏蔽环路,减少EMI干扰;模拟信号走线需远离数字信号走线(间距>3mm),避免数字噪声耦合。

• 接地设计:单点接地+完整地平面:

地环路是共模噪声的主要来源,需规范接地设计:

1.ADC的AGND与DGND在PCB上单点连接(如通过一个0Ω电阻或直接短接),避免形成地环路;所有模拟电路的接地都汇聚到AGND,数字电路接地汇聚到DGND,再通过单点连接。

2.为ADC单独划分模拟地平面,确保AGND平面完整,无其他信号线穿越;模拟地平面与数字地平面的重叠区域需最小化,减少相互干扰。

• EMI防护:抑制干扰源+增强抗干扰能力:

针对电磁干扰,需从“抑制干扰源”和“增强ADC抗干扰能力”两方面入手:

1.在ADC输入线、VREF线上串联磁珠(如100Ω@100MHz),抑制高频干扰;若存在静电风险,可在输入引脚旁并联TVS管(如SMF05C),保护ADC不受静电损坏。

2.若PCB上有功率模块(如电机驱动、射频模块),需在其与ADC之间增加金属屏蔽罩(如屏蔽盖),减少辐射干扰;功率模块的开关节点需并联缓冲电容,抑制开关噪声。

四、总结

ADC增益误差是影响数据采集精度的关键因素,其本质是实际增益与理想增益的偏差,可通过绝对误差、相对误差(%FS)和LSB误差三种形式量化。

误差来源分为芯片自身固有误差(制造工艺、温度漂移等)和PCB板级外部误差(电源噪声、布线缺陷等),需采用“选型规避+设计优化”的组合策略:通过选择校准型、低温度系数、高PSRR的ADC,搭配外置高精度参考电压,从源头降低固有误差;通过独立电源、规范布线、单点接地和EMI防护等PCB设计手段,消除外部干扰。

在实际工程中,需结合系统精度需求,平衡成本与性能,制定针对性的误差控制方案,确保ADC发挥最优性能。而德思特 ADC/DAC 测试系统作为专业的 ATE 芯片测试平台,能够为 ADC 增益误差的精准评估提供高效、可靠的测试方案,助力工程师打造更高精度的数模转换产品。

- 相关产品

• 德思特ADC/DAC自动化测试系统

德思特ADC/DAC测试系统是一套9槽ATE芯片测试平台,模块化设计确保灵活性与扩展性,专注于数模及模数转换芯片的深度测试。系统囊括ADC/DAC全范围线性动态评估,搭载DIO时钟同步模块,可测8-24 bit ADC/DAC,以高达400 MHz的采样速率,重塑高效芯片测试新标准。

德思特ADC、DAC芯片测试白皮书

- 精准术语解释:20+关键ADC术语全解析,全面理解采样、抖动、非线性误差等影响性能的核心因素。

- 全流程参数计算:静态参数、动态分析、ENOB / SNR / SFDR / THD等核心指标计算方法详尽剖析。

- 实例操作指导:涵盖AD7671 / AD9244 / LTC2641等多种芯片真实测试配置与操作流程指导。