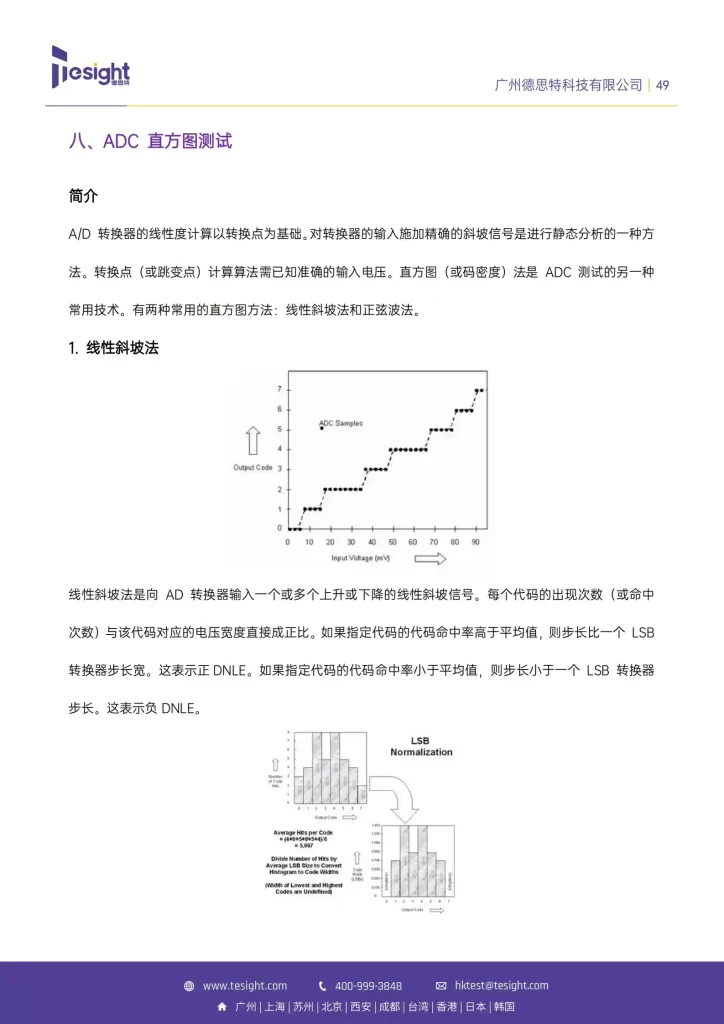

在之前发布的内容中,我们为大家介绍了ADC芯片的“基本功”测试——静态参数,并以斜坡测试(Ramp Test) 为核心,手把手详解其工程文件的配置要点。

德思特干货 | 解锁 ADC 真实性能:斜坡测试(Ramp Test)硬件配置关键指南

本期内容将深入斜坡测试的软件配置实战,带您一步步解析工程文件的设置秘诀,让测试数据精准呈现。

软件配置分为上位机与下位机两个部分。下位机软件已经预装在德思特 ATX 测试系统的嵌入式计算机内,确保了即开即用的便利性。用户仅需连接电源线和网线,按下开机按钮,系统便会自动执行程序的启动、硬件上电自检和初始化过程。

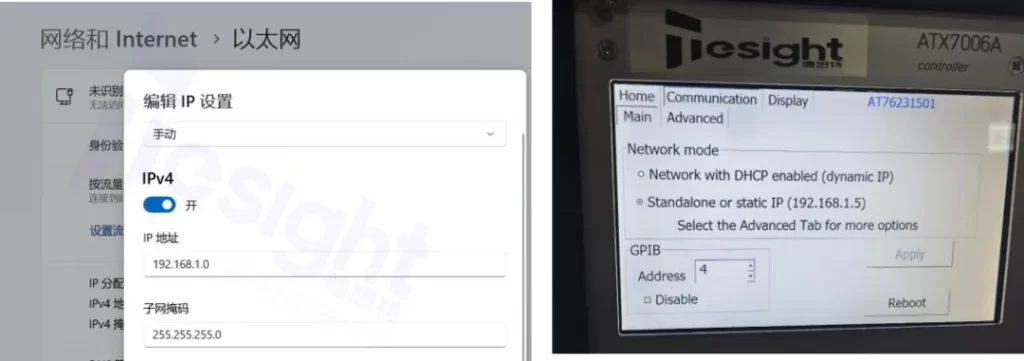

对于下位机软件的配置,通常情况下,我们只需通过触控屏调整网络设置参数。最快捷的方式是启用DHCP,让系统自动获取 IP 地址,用户只需记录下分配到的 IP 地址即可。如果需要更稳定的网络环境,也可以手动设置一个固定的 IP 地址。

静态 IP 地址需要同时设置 PC 端以太网的 IP 地址和设备 IP 在同一个网段下。

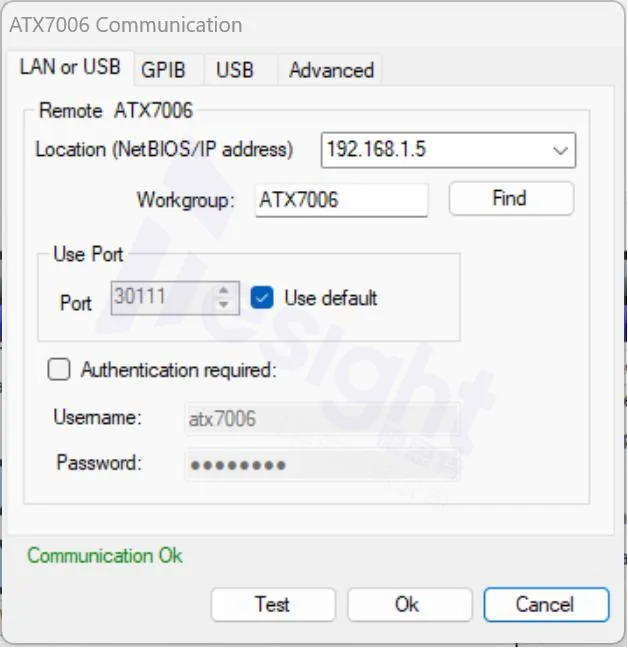

至于上位机软件——ATView7006,也会作为标准交付内容之一提供给用户,无需额外进行订购。我们只需要找一台装有 Windows 系统的电脑,通过交付内容中配套的资料光盘进行安装即可,如果电脑缺少光驱,也可以联系德思特获取数字版安装包和其他资料。安装后,我们进入软件,在通讯配置面板中填入刚才确认到的 IP 地址,点击“Ok”按钮,即可完成与下位机的连接。

1.新建项目文件

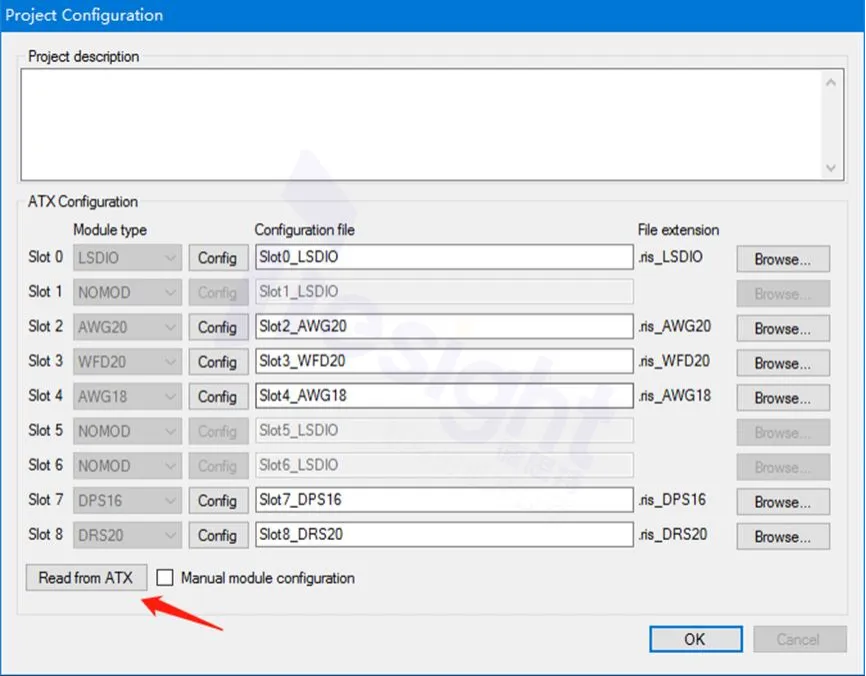

连上设备,我们就可以在软件中执行新建项目。在创建好相关项目文件后,软件会自动弹窗让我们配置下位机有什么硬件模块,一般情况下,我们并不需要手动配置,只需要点击“Read from ATX”按钮,上位机便会跟下位机进行通讯,自动获取相关硬件信息。

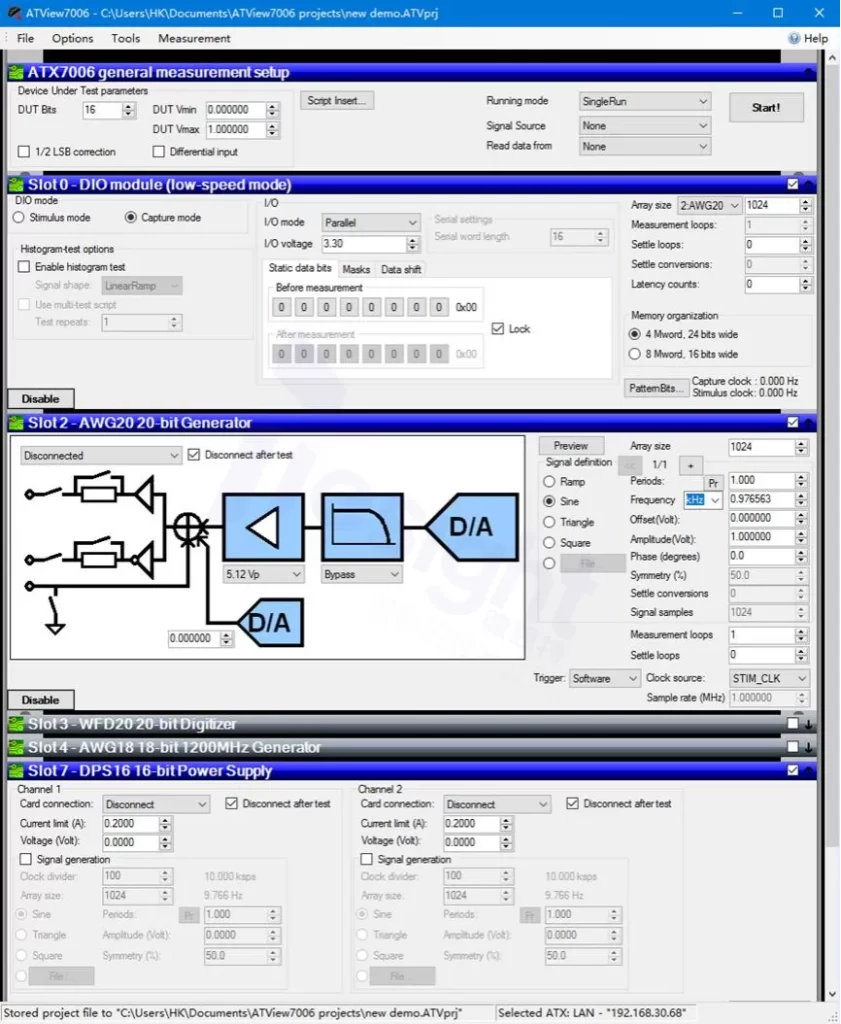

按“OK”按钮后,软件主界面便会自动增加每个硬件模块对应的控制面板。我们也可以通过手动取消勾选的方式,来禁用部分在本次测试中不需要用到的硬件模块。比如下图中的 WFD20 数字化仪模块(用于DAC 测试)以及 AWG18 模块(用于其它 UUT 的另一个 AWG)的相关控制面板就已经被笔者禁用并折叠了。

2.测试概览设置

完成项目文件的创建后,我们首先需要确认待测 ADC 的输入情况,并告诉软件我们打算用哪个模块作为主要的信号输出输入模块,来开展这次测试。

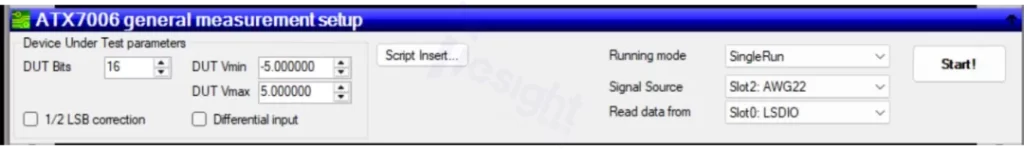

前文已经提到,我们作为示例的 AD7671 分辨率为 16 位,采用单端输入,并且当前选用的输入量程档位对应的电压是-5 ~ +5 V。因此我们将相关信息填入,如下图所示。

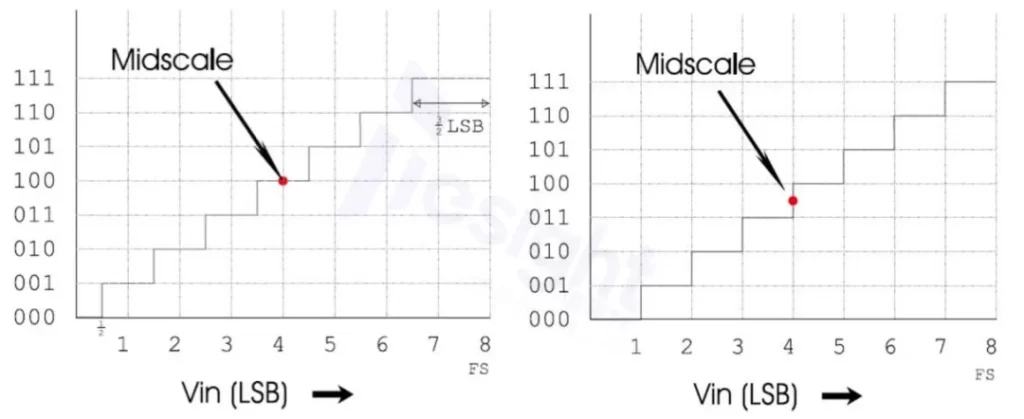

其中值得一提的是,我们提供了一个 1/2 LSB 校正的选项,该选项适用于那些第一个 LSB 设计宽度只有其他 LSB 一半的 ADC 或 DAC 使用,开启后会自动改变理想转换曲线,并根据这种情况修正各种线性、非线性误差的计算。经过我们核实,AD7671 并不属于这种情况,因此我们没有实际勾选该选项。

常见的 DUT 都是左侧格式,也就是采集到的数据点均在中值,不需要 1/2LSB 的偏移,一般手册上未提及就不需要勾选;而对于右侧的,需要将输入信号进行偏移对齐到中点,所以才要勾选。

3.DIO模块设置

我们按前面给出的软件设置界面从上往下顺序看,第二个设置板块就是 DIO 模块。在 ADC 测试中,DIO 模块扮演着关键角色:对外,它负责与 ADC 的通信,提供必要的时钟信号、采集触发信号、状态配置等,并接收转换后的数字码;对内,它作为时序指挥中心,控制任意波形发生器(AWG)的更新时机。德思特 ATX 测试系统正是利用了 DIO 模块的这些功能,精确满足了斜坡测试对设备间时序协调的严格需求。

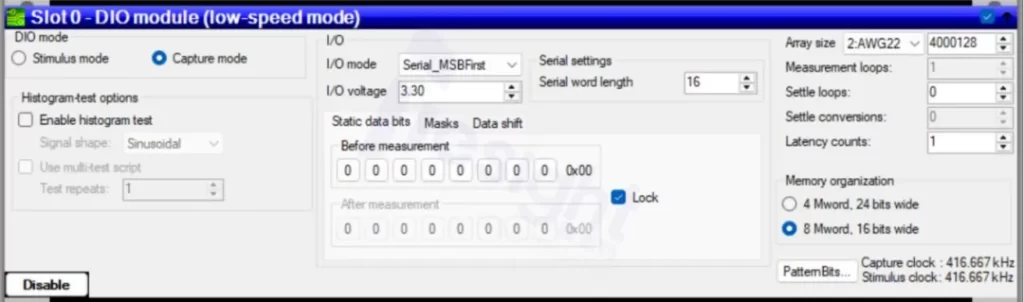

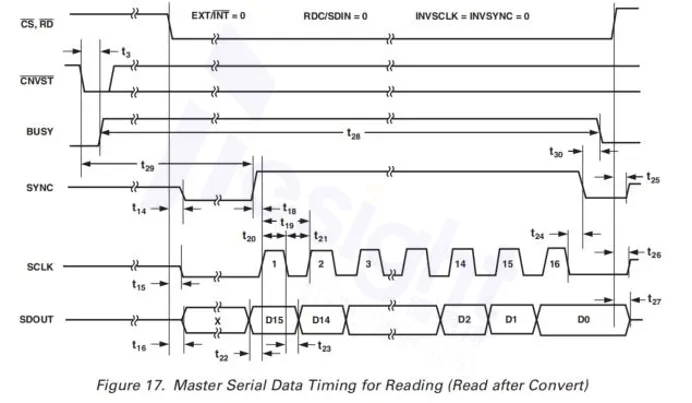

首先,我们确认我们的 UUT 通讯方式和电平,这些信息我们可以从 AD7671 的官方数据手册中获取。

这里我们按手册的要求,设置 3.3V 的 IO 电压、MSB 串行通讯的 IO 模式,以及 16bit 的字长。

在 I/O 大类下,我们还提供了 3 个设置选项卡:分别是 Static data bits、Masks 和 Data shift。其中 Static data bits 用来控制 8 个静态数字输出口;Masks 用于设置位掩码,可以将某些指定位忽略或者置反,这对于某些具有特殊输出规则的情况会派上用场;Data shift 则是对测试结果按位左移或右移,主要适用于在最高位或最低位有无效位输出的 UUT。

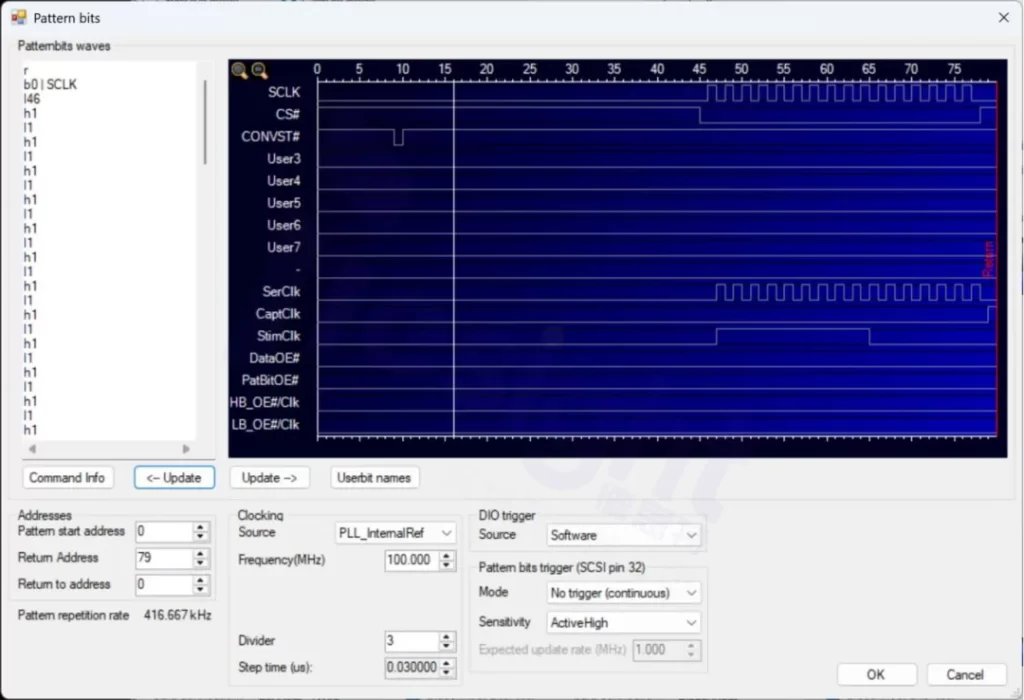

接下来是 DIO 模块设置的重头戏——时序设置部分。我们只需要点击右下角的“Pattern Bits…”按钮即可打开一个新的时序设置面板窗口。在这里,可以通过手动调节窗口内的时序图,控制 DIO 模块对内对外的各个信息。在本示例当中,这些信号包括了提供给 ADC 的 SCLK 时钟信号、CS#使能信号以及CONVST#转换开始信号;也包括了采集侧的串行位移信号 SerClk、采集锁存信号 CaptClk、AWG 输出时钟信号 SimClk。此外,我们还能通过调节 PLL 频率以及分频系数决定时序图中每一格对应的时间长度。

其中,输出到 ADC 的信号波形和 PLL 时钟参数,可以由 UUT 数据手册中关于时序部分的要求决定;对内的各种触发信号,则需要依据所选用 AWG 模块对应的手册说明内容决定。由于篇幅限制,此处不展开说明,相关手册可向德思特索取。

有部分细心的读者可能发现了:控制 AWG 刷新的 StimClk 信号时序位置晚于控制 ADC 开始转换的CONVST#信号,这样不会导致 ADC 本次转换得到的是 AWG 的上一个输出值对应的结果吗?关于这个问题,我们实际上可以通过设置 DIO 模块参数的“Latency counts”来解决,该参数设为 1 即表示,DIO 需要提前多获取一个周期的数据并将其丢弃,从第二个周期开始的数据才采用,并且后续软件处理中,采回的数据会自动对应回 AWG 第一个周期的电压。这个功能也适用于一些具有流水级或其他原因导致输出具有周期延迟的 ADC。

还有读者可能会疑惑,StimClk 信号是处于串行读出阶段的,这样不会有相互冲突吗?实际上这个也是一个优化的小技巧,根据 UUT 数据手册的描述,ADC 转换实际上只在 CONVST#信号到达之后的一段时间内进行,在其之后的串行数据读出阶段到下一次 CONVST#信号到来之前,输入电压改变实际上并不会有任何影响,因此把 StimClk 信号放在串行读出阶段,可以显著缩短整个时序周期的长度,从而提升最高测试采样率和测试效率。

完成了DIO模块的精细配置,ADC与测试系统间的“对话”规则已然确立。然而,精准的时序控制只是基石,要为ADC提供纯净且稳定的激励源与工作环境,我们还需将目光投向任意波形发生器(AWG)与电源模块。下一期内容,我们将继续深入软件配置的下半场,详细解析“AWG设置”与“电源设置”的关键参数,并最终带领大家“开始测试与查看结果”,见证数据从波形生成到精准采集的全过程。

- 相关产品

• 德思特ADC/DAC自动化测试系统

德思特ADC/DAC测试系统是一套9槽ATE芯片测试平台,模块化设计确保灵活性与扩展性,专注于数模及模数转换芯片的深度测试。系统囊括ADC/DAC全范围线性动态评估,搭载DIO时钟同步模块,可测8-24 bit ADC/DAC,以高达400 MHz的采样速率,重塑高效芯片测试新标准。

德思特ADC、DAC芯片测试白皮书

- 精准术语解释:20+关键ADC术语全解析,全面理解采样、抖动、非线性误差等影响性能的核心因素。

- 全流程参数计算:静态参数、动态分析、ENOB / SNR / SFDR / THD等核心指标计算方法详尽剖析。

- 实例操作指导:涵盖AD7671 / AD9244 / LTC2641等多种芯片真实测试配置与操作流程指导。