上一期内容中,我们为大家介绍了如何调整DDS设置。本期德思特将带大家进一步深入,解析固有频率与幅度斜率的相关知识,并探讨频率与幅度斜率中存在的量化误差——包括时间量化误差、行为时间误差以及值量化误差。掌握这些概念,将帮助我们更全面地理解信号生成的精确性与稳定性。

一、固有频率和斜率频率说明

除了频率、幅度和初始相位之外,德思特DDS 模块还支持线性频率和幅度斜率作为动态参数。

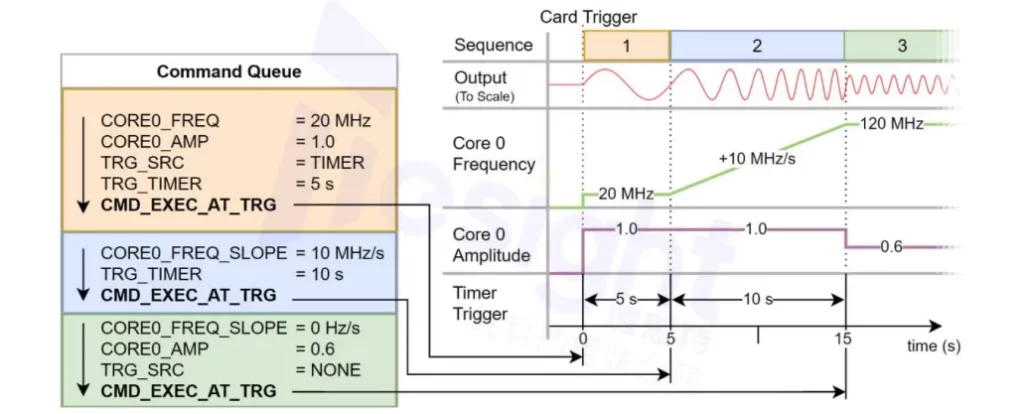

序列顺序

- 初始重置后:所有参数设置为 0,触发源设置为外部卡触发器。

- 在卡触发事件时:将频率设置为 20 MHz,幅度设置为 1.0。为了在 5 秒后切换到下一个序列,将触发源设置为内部定时器,该定时器开始计时到 5 秒,此时触发下一个序列。

- 核心频率:以 10 MHz/秒的线性平稳速率增加。因此,10 秒后达到最终频率 120 MHz。

- 通过将斜率设置为 0 来停止斜率,同时将幅度设置为 0.6。最后,将触发源设置为 NONE,这将禁用内部定时器。

二、斜率量化机制与误差

虽然斜率实际上是线性的,但它们是在卡的逻辑中以离散步骤计算的,具有量化的时间和值分辨率。对于TS-66xx DDS 模块,最小斜率刷新速率 t_re 为 6.4 ns,这对于它们设计的大多数应用来说绰绰有余。

由于这些量化的计算,斜率增量和时间分辨率是有限的,并且可能在实际值和所需设置值之间存在一定的量化误差。

通常,这些效果仅在异常长的斜率(其最小斜率步长达到)或短斜率(其时间量化变得相关)的顺序为秒时才可见。为了减轻这些效果,应在斜率结束时手动设置最终频率。

1.时间量化误差

当为定时器输入一个浮点值时,驱动程序会将其舍入到 t_re 步长的完整时钟周期,从而创建时间误差。对于约 1 毫秒长的斜率,此量化误差在 +/- 3.2 ns 或 3.2 ppm 的范围内,对于许多应用来说可以忽略不计。可以通过在您的应用程序和编程中考虑此量化,并且只使用 t_re 步长的时间周期来减轻它。

2.行为时间误差

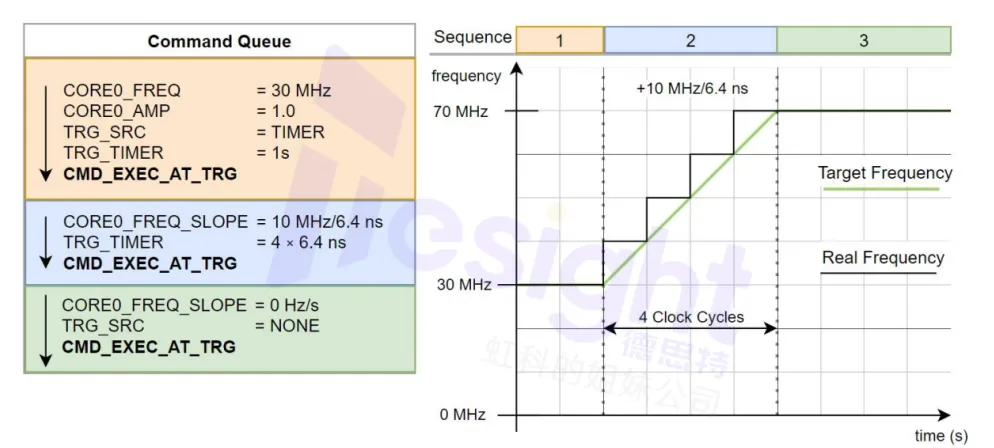

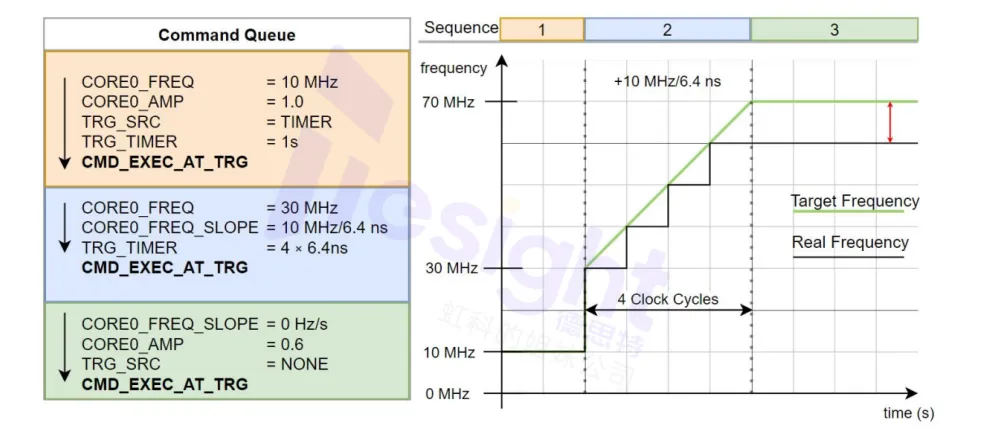

此外,还可能发生另一种时间误差:如果仅在执行事件处有斜率命令,则频率将与触发事件同时增加,导致预期的最终频率,如图1所示。

然而,当在同一个执行事件中设置频率和斜率速度时,首先在第一个时钟周期设置频率,然后频率在下一个时钟周期增加,如图 2所示。虽然这种行为在技术上并不错误,但因此斜率比预期短一个时钟周期 t_re。这种行为可以通过显式设置最终频率或通过增加一个增量调整起始频率来轻松解释,如图3所示。

请注意,为了显示目的,选择了一个非常短的斜率周期为 4 个时钟周期,目前还不可能使用EXEC_AT_TRIG 命令,因为最小定时器时间在 100 ns 的范围内。对于毫秒数量级的斜率周期,这种影响在百万分之几的范围内。

3.值量化误差

为了减少值误差, 斜率在内部以比DDS的频率分辨率fstep更高的斜率fstep分辨率进行计算。 对于持续时间在秒量级的较长时间,可以设置一个步进除数,进一步提高分辨率,但通常对于毫秒时间尺度内的应用程序来说并不需要。

fstep可以通过读取API中的寄存器SPCDDS AVAILFREQ_SLOPE STEP来读取, fstep可以通过读取寄存器SPC_DDS_AVAIL_FREQ_STEP来读取。

示例:

德思特66xx DDS模块具有大约0.3 Hz的频率分辨率fstep。 如果您将斜率速度设置为fstep/tre,则频率每6.4 ns会 增加exactly 0.3 Hz。 如果这也将是最小频率斜率分辨率fstep,则低于0.3 Hz/6.4 ns的斜率值将不可能,并且不会执行任何斜率。

因此,在一秒钟后, 只能进行量化频率变化0Hz、47 MHz、 2*47 MHz、 3*47 MHz等。

4.总结

为了计算最大频率斜率量化误差, 只需将斜率分辨率乘以斜率持续时间。 我们除以2, 因为我们向上或向下舍入到值之间的值:ferror=fstep·△t/2

实际实现的频率斜率分辨率fstep高于fstep,fstep=694 Hz/s。 因此, 如果您想在 1毫 秒内从1 MHz增加到2MHz,您将最终获得最大误差为fstep ·△t /2 = 0.348 Hz, 这对于其设计的大多数应用程序来说可以忽略不计。

END

本期我们带大家解析了固有频率与幅度斜率的相关知识,并探讨了其中涉及的量化误差——包括时间量化误差、行为时间误差与值量化误差。下期我们将进入相位偏移模式的内容,精彩继续,干货不容错过,敬请期待!

- 相关产品

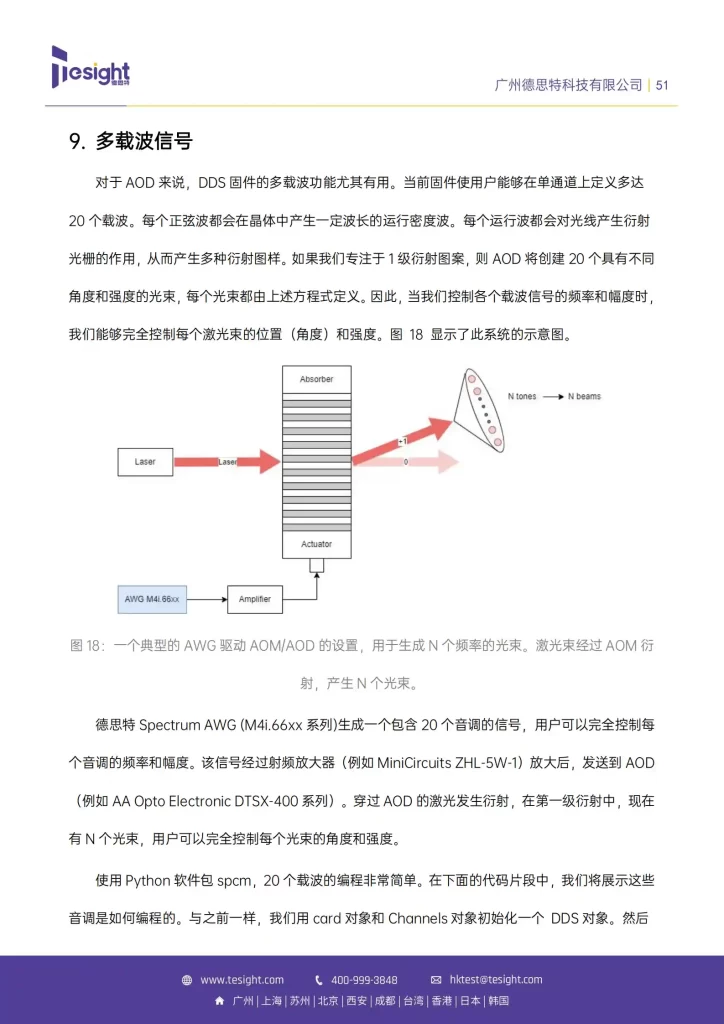

• 德思特板卡式AWG和DDS

- 快速16位DAC,带基于FPGA的DDS

- PCIe、PXIe或以太网可选,最多24个通道

- DDS频率DC至200MHz

- DDS命令可以以6.4ns的间隔发出

- 固定触发到输出延迟

- 输出电平±80mV至±2.5V,50Ohm

- 本机DDS命令:频率、幅度、相位、频率斜率、幅度斜率、等待触发、数字输出

- 巨大的板载内存,每4个通道可容纳5.12亿个DDS命令

德思特AWG DDS模式应用白皮书

- 精准术语解释:DDS 与 AWG 模式核心技术对比全解析

-全流程参数配置:DDS 核心参数设置与行为控制详尽指导 -实例操作指导:量子操控、AOM/AOD 驱动与多音信号生成实战

- 底层编程接口详解:寄存器级调用与硬件控制流程图解