在之前发布的内容中,我们从上下位机连接、工程新建到DIO模块时序设置,详解了斜坡测试软件配置实战,为捕捉ADC静态性能奠定基础。

德思特干货 | 解锁 ADC 真实性能:斜坡测试(Ramp Test)软件配置实战

本期,德思特将带您继续深入学习 斜坡测试 (Ramp Test)的软件配置,详细拆解从AWG配置到结果分析与总结,帮助工程师高效系统掌握斜坡测试软件配置的全流程。

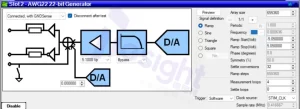

一、AWG配置

AWG 部分的配置允许用户定义测试激励信号的具体形式和参数,并提供了调整信号前端处理工作参数的选项。配置界面的左半部分采用了简化的原理图形式,直观展示了 AWG 的结构,这不仅帮助用户理解其硬件功能,还清晰地指示了各个参数的实际影响,有效降低了用户的学习门槛。

1、连接方式

- 本示例中选择“Connected, with GND Sense”

- 适用场景:UUT输入电阻为高阻

- 原理图显示该选项短路了50Ω输出负载电阻

- 断开与输出近端地的连接

- GND反馈线延伸至待测芯片附近,可有效针对浮地问题进行补偿反馈,提高测试精度

2、AWG内部结构认知

从原理图可知,AWG内部有两个DAC:

- 主DAC:负责波形的产生,信号随后通过滤波器和调整幅值的放大器

- 次DAC:负责生成高精度的DC偏置信号(本示例中偏置设为0V)

放大器选项中的5.1 Vp指的是峰-峰值的一半,意味着输出最高电压距离直流基线最高可达5.1V,配合0V偏置可产生-5.1V到+5.1V电压。

3、Array size 的精确计算

Array size(阵列大小)决定测试精度:

- 16位ADC共有65536个LSB

- 若设置4×65536个采样点,DNL分辨率仅1/4 LSB = 0.25 LSB

- 因此可根据所需DNL分辨率推算倍数(例如需要0.1 LSB精度,倍数需≥10)

此外,实际测试中还可能受到随机噪声的影响,需要额外增加采样点以通过平均抵消噪声,同时Ramp测试的电压应略微超出ADC的输入范围,也会造成额外开销。

通用建议:Array size设置为 10×2^N ~ 32×2^N(N为ADC分辨率位数)。

4、斜坡信号的电压范围设定

由于实际待测芯片的转换范围可能与标称范围存在细微差异,设置的斜坡信号起始电压应稍低于最低标称值,终止电压应略高于最高标称值:

- 本示例设定为 -5.05V 到 +5.05V

- 使得对UUT实际转换范围偏差的测量成为可能

- 德思特设计AWG前端放大器时选择5.1Vp而非5Vp,正是出于同样的考量——在尽可能不影响输出精度的前提下,允许波形幅值略微超出标准量程

5、预览功能

配置面板顶部提供了预览按钮,可快速查看预计输出的波形图样,帮助确认幅值、周期等关键参数,有效预防由于配置失误导致的UUT损坏。

二、电源设置

电源部分的设置相对简单。

只需将电压值分别输入到对应模块的输出电压设置栏即可。为了实现更高的电压输出精度,使用4线制连接方式,建议条件允许时采用。

本示例中:

- DPS16模块:为UUT提供5V供电

- DRS20模块:输出2.5V参考电源

三、开始测试与结果分析

1、一键启动

保存项目文件(便于下次快速调用),点击软件顶部的“Start !”按钮,即可开始自动化测试和分析流程。

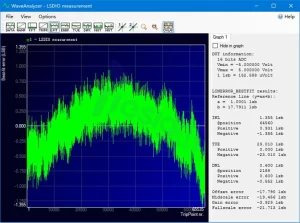

2、结果解读

测试完成后,结果以弹窗形式呈现。用户可点击工具栏中的各个视图按钮查看不同分析结果:

- B.FIT视图:显示最佳拟合直线下的INL、TUE、DNL等参数

- 本示例测得INL为1.355 LSB,符合AD7671数据手册标称的±2.5 LSB Max

- 可利用放大镜、光标等工具观察细节

- 支持导出结果图、计算数据和原始采集数据,便于进一步分析

化繁为简,精准高效

通过本文的介绍,我们完成了ADC静态参数测试中 斜坡测试 方法的软件配置全流程的学习。

这一流程为ADC静态参数测试提供了一种高效、精确且用户友好的解决方案,帮助工程师更加专注于产品设计开发的核心环节,加快产品上市时间,确保产品的高质量和性能。

下期预告:我们将深入ADC芯片动态参数测试的软件配置实战,带您一步步解析正弦波拟合测试法的工程文件设置秘诀,让动态性能评估精准可靠。

- 相关产品

• 德思特ADC/DAC自动化测试系统

德思特ADC/DAC测试系统是一套9槽ATE芯片测试平台,模块化设计确保灵活性与扩展性,专注于数模及模数转换芯片的深度测试。系统囊括ADC/DAC全范围线性动态评估,搭载DIO时钟同步模块,可测8-24 bit ADC/DAC,以高达400 MHz的采样速率,重塑高效芯片测试新标准。

德思特ADC、DAC芯片测试白皮书

- 精准术语解释:20+关键ADC术语全解析,全面理解采样、抖动、非线性误差等影响性能的核心因素。

- 全流程参数计算:静态参数、动态分析、ENOB / SNR / SFDR / THD等核心指标计算方法详尽剖析。

- 实例操作指导:涵盖AD7671 / AD9244 / LTC2641等多种芯片真实测试配置与操作流程指导。