在硬件PCB设计中,电容选型与搭配直接决定电路供电稳定性——尤其对于德思特ADC/DAC测试系统这类对电源纹波、高频响应要求严苛的精密设备,错误的电容组合可能导致信号失真、测试精度下降,甚至影响核心器件寿命。

新手常困惑:电解电容和MLCC电容该怎么选?为何芯片输入端必须 “电解去纹波 + MLCC 降 ESR”?本文将拆解两者核心差异、搭配逻辑,并针对性给出其在德思特ADC/DAC测试系统中的适配方案,帮你快速掌握全频段滤波选型技巧。

一、ESR和ESL到底是什么?

1.ESR(等效串联电阻):

理想电容无电阻,但实际电容的电极、电解液、引脚会带来微小电阻。ESR越大,滤波时能量损耗越多,高频纹波 “过滤不干净”,还可能发热影响稳定性—— 这对 ADC/DAC测试系统的信号采集精度是致命影响(纹波会叠加在测试信号中,导致数据偏差)。

2.ESL(等效串联电感):

实际电容的引脚、电极结构会形成微小电感。ESL越大,高频下响应速度越慢(充放电跟不上MHz级电流波动),相当于 “高频时失效”—— 而ADC/DAC测试系统的高速信号处理场景(如高频模数转换),恰好对电容的高频响应能力要求极高。

二、电解电容与MLCC电容:核心差异与互补逻辑

1.电解电容的优势与短板

- 优势:电解电容容量大(通常为μF级),能高效存储电荷,专门针对低频纹波(1kHz 以下),相当于 “大水库”,稳定供应大基础电流。

- 短板:ESR较高(通常几十到几百 mΩ),高频时ESR还会进一步上升,导致高频纹波(1kHz以上)过滤效果差;同时ESL也比MLCC大,高频响应慢。

2.MLCC的 “互补作用”

- 低ESR特性:MLCC的ESR极低(通常几mΩ甚至更低),能快速衰减高频纹波,解决电解电容 “过滤不干净” 的问题。

- 低ESL优势:MLCC封装小、引脚短,ESL远小于电解电容,高频响应速度极快(能跟上 MHz 级的电流波动),相当于 “高频小水库”,瞬间响应需求。

3.协同效果

电解电容负责滤除1kHz以下的低频纹波,MLCC针对性滤除1kHz以上的高频杂波,两者结合后,电路的总ESR大幅降低,全频段纹波都能被有效抑制,供电电压更平稳。当负载电流突变时,电解电容通过大容量储能快速补充电流,MLCC则以更快的充放电速度响应高频电流波动,共同维持供电电压的平稳。

三、ESR/ESL关键影响速查表

频率越高,ESR和ESL的影响越明显,这也是高频场景(如芯片供电)必须搭配MLCC的原因。

电解电容选 “低ESR型”(如固态电解),搭配MLCC后,整体滤波效果会更优。

补充关键说明

- ESR超标信号:电路纹波值高于设计值、电容发热明显,多是ESR过大导致,需增加MLCC并联或更换低ESR电解电容。

- ESL降低技巧:缩短电容引脚长度、采用小封装MLCC、多颗同容量MLCC并联,均能有效降低总 ESL。

- 材质影响:MLCC选X7R/X8R材质,ESR和ESL稳定性优于Y5V/Z5U;电解电容选固态类型,ESR远低于普通液态电解。

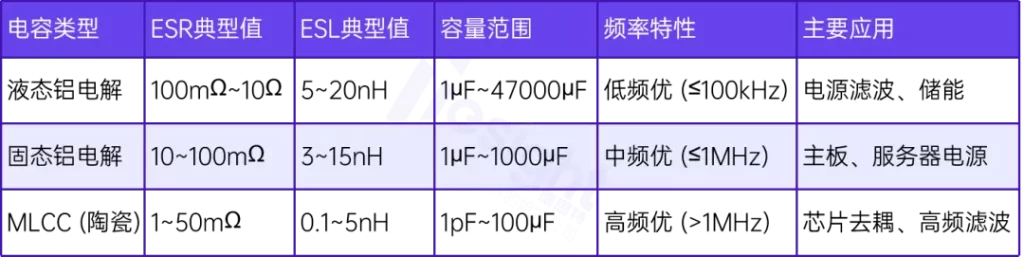

三、三大类电容ESR/ESL核心参数对比

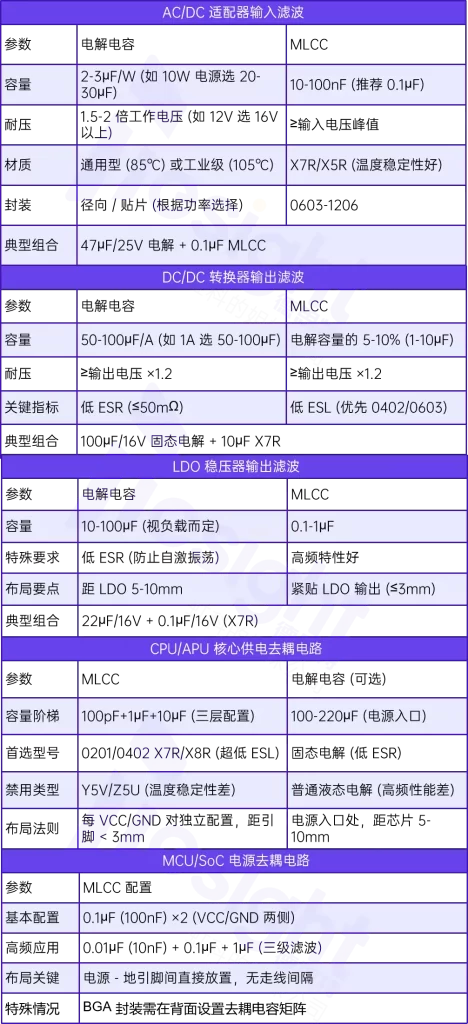

四、电解电容 + MLCC常见应用场景下的选型

1.实用选型速查表

2.选型关键决策树

①确定主要纹波频率

- <100kHz → 优先液态电解

- 100kHz~1MHz → 固态电解

- 1MHz → MLCC 为主

②根据纹波电流选择

- 纹波电流 > 1A → 液态 / 固态电解 (ESR<50mΩ)

- 纹波电流 <1A → MLCC (ESR<10mΩ)

③温度环境考量

- 85℃ → 固态电解或 X7R/X8R MLCC

- 125℃ → C0G/NP0 MLCC 或军工级固态

3.布局黄金法则

- “电源入口→电解电容→MLCC→芯片” 级联布局

- 高频MLCC必须紧贴芯片 (≤3mm), 电源 – 地之间直接连接

- 大电容间距≥3倍本体宽度, 避免热干扰

- 多层板中: 电源平面与地层紧邻,减少环路电感

4.参数选择要点

- 电解电容耐压: ≥工作电压×1.5 (高压应用×2)

- MLCC耐压: ≥工作电压×1.2 (高频应用×1.5)

- 温度降额: 工作温度≤额定温度×0.8 (高温环境×0.7)

- 纹波电流: 电解电容实际纹波≤额定值×0.7,MLCC可适当放宽

五、总结

电解 + MLCC搭配本质是优势互补:电解电容凭借大容量处理低频纹波,MLCC以超低ESR/ESL解决高频滤波。选择时需根据频率、纹波电流和温度,优先考虑总ESR<目标纹波电压/最大纹波电流,同时确保MLCC的自谐振频率>电路最高工作频率。

- 相关产品

• 德思特ADC/DAC自动化测试系统

德思特ADC/DAC测试系统是一套9槽ATE芯片测试平台,模块化设计确保灵活性与扩展性,专注于数模及模数转换芯片的深度测试。系统囊括ADC/DAC全范围线性动态评估,搭载DIO时钟同步模块,可测8-24 bit ADC/DAC,以高达400 MHz的采样速率,重塑高效芯片测试新标准。

德思特ADC、DAC芯片测试白皮书

- 精准术语解释:20+关键ADC术语全解析,全面理解采样、抖动、非线性误差等影响性能的核心因素。

- 全流程参数计算:静态参数、动态分析、ENOB / SNR / SFDR / THD等核心指标计算方法详尽剖析。

- 实例操作指导:涵盖AD7671 / AD9244 / LTC2641等多种芯片真实测试配置与操作流程指导。