在进行测试系统设计与调试时,工程师们经常面临诸多技术挑战:如何正确使用68pin接口?信号通信接口是否支持SPI协议?哪些外围电路是必须的?电源纹波应该如何控制?

本文系统梳理了测试系统设计中六个最关键的技术问题,从接口定义到电路保护,从信号协议到电源设计,为您提供详尽的解答和专业建议。无论您是正在设计测试板卡,还是优化现有测试系统,这篇文章都将为您提供实用的技术参考。

一、接口详解:功能与规格全解析

问:参考设计中的德思特68pin接口是什么类型的连接器?其主要功能是什么?

答:这是DIO通信专用的68pin SCSI连接器,作为测试系统与待测器件之间的通信桥梁。该接口负责传输ADC的时序信号、时钟信号以及使能信号等关键信号。

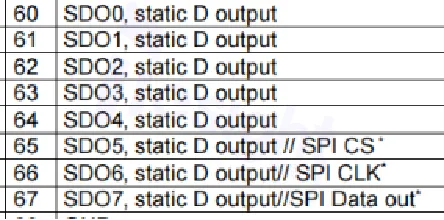

关于德思特ATX中对于该接口的说明如下图所示:

1-20可用于并行数字信号输入/输出。24-31为pattern bit输入端口, 用于输出时序波形信号,如触发转换、时钟信号输出、控制数据输入 / 输出时序。60-67为静态码值输入端口,可以用于输入固定电平来使能芯片工作状态选择端口。

二、通信接口能力:协议支持与扩展功能

问:68pin中信号通信接口是否为I/O口,这些接口是否是带协议的,是否可以用于SPI联动通信?

答:DIO接口在板卡设计阶段已经固定端口类型。其中模式位(pattern bit)支持可配置波形输入,特别预留了8个自定义时序输入端口。这8个灵活的模式位端口可以通过配置实现I2C、I2S、SPI等复杂通信协议。

三、外围电路设计:必要性分析与设计建议

问:参考设计中的输入部分外围电路有什么作用?继电器电路的功能是什么?在设计测试板时这些电路是否可以简化?电源输入部分的外围电路又有什么作用?

答:输入部分的外围电路是针对AD7671芯片设计的驱动和滤波电路,这些电路是按照ADI芯片手册的建议设置的。在实际应用中,如果待测芯片不需要驱动电路,可以酌情简化。

继电器电路实际上是一个模式切换模块。如果待测芯片的工作模式比较简单,可以直接使用静态位控制结合上位机软件进行模式配置。

电源输入部分的外围电路主要提供过压保护功能。当电源电压出现异常波动时,过压指示灯会亮起,确保待测芯片的安全。现有的两个参考设计都采用了过压保护电路,为了保证测试安全性和芯片的长期可靠性,建议保留过压保护电路。

四、电源质量要求:纹波控制与噪声管理

问:测试系统对电源纹波有什么具体要求?

答:我们的电压源和测试机台电源都经过专业的降噪处理,电源噪声已经被控制在很低的水平。特别值得一提的是,DRS和DPS电压源都采用线性电源设计,从根本上避免了开关电源带来的高频纹波,实际纹波水平几乎可以忽略不计。

五、设计注意事项:信号完整性与滤波设计

问:在测试板设计中还有哪些需要注意的事项?差分输入是否需要对称滤波?

答:关键注意事项包括:

- DIO数字接口需要添加RC滤波电路

- 空闲引脚需要接地

- 模拟域和数字域需要严格分离

- DPS和DRS需要采用四线制接法,特别注意检测线的连接

- 差分信号必须使用对称的RC电路来保持差分结构的完整性

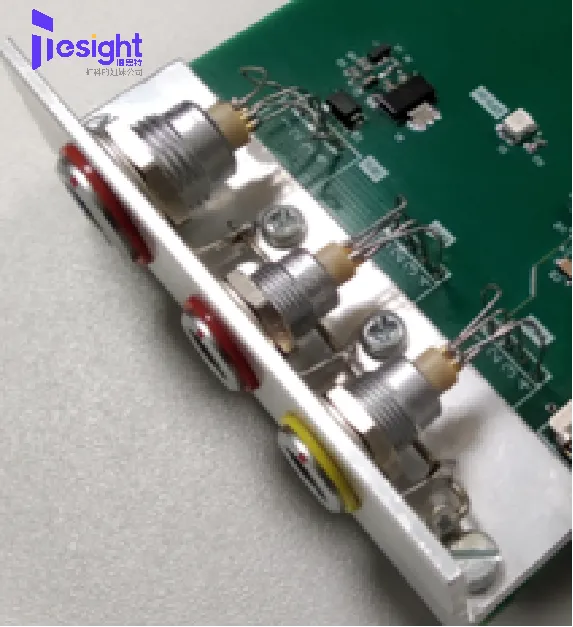

六、电源接口配置:扩展能力与连接方案

问:DPS和DRS接口的配置是怎样的?如果待测芯片需要多路电压源,是否能够满足要求?

答:DPS和DRS都是双通道设计,最多可同时提供两路电压源和两路参考电平,对于大多数ADC测试应用来说完全足够。如果需要更多电压源,可以通过增加供电板卡来实现,测试机台提供的九个槽位为系统扩展提供了充足的空间。

关于lemo连接器到PCB的连接,可以直接采用跳线连接方式,这些连接工作可以在PCB制造和组装阶段由工厂完成。

- 相关产品

• 德思特ADC/DAC自动化测试系统

德思特ADC/DAC测试系统是一套9槽ATE芯片测试平台,模块化设计确保灵活性与扩展性,专注于数模及模数转换芯片的深度测试。系统囊括ADC/DAC全范围线性动态评估,搭载DIO时钟同步模块,可测8-24 bit ADC/DAC,以高达400 MHz的采样速率,重塑高效芯片测试新标准。

德思特ADC、DAC芯片测试白皮书

- 精准术语解释:20+关键ADC术语全解析,全面理解采样、抖动、非线性误差等影响性能的核心因素。

- 全流程参数计算:静态参数、动态分析、ENOB / SNR / SFDR / THD等核心指标计算方法详尽剖析。

- 实例操作指导:涵盖AD7671 / AD9244 / LTC2641等多种芯片真实测试配置与操作流程指导。