在深入探讨新型 DDS(Direct Digital Synthesis,直接数字合成) 模式的各项特性之前,我们先回顾德思特 Spectrum 信号发生器设备传统上运行的 任意波形发生器 (AWG) 模式。

一、传统AWG模式

在传统 AWG 模式下,用户需预先计算所需输出波形的每一个样本点,并将其上传至 AWG 的板载内存。随后,根据所选子模式(如标准重放、FIFO 或序列模式),这些数据可被一次性播放、循环播放或以连续流方式输出。理论上可生成任意类型的波形,灵活性极高,适用于多种复杂应用场景。

1.内存与采样率需求

为支持高采样率下的长序列波形存储,AWG 需配备大容量板载内存。例如:M5i.63系列 AWG 卡

-

- 最大采样频率:10 Gs/s

-

- 最大板载内存:8 GS

-

- 以10GS/s采样率可存储超过800ms的超高速波形数据

2.高速数据传输支持

所有德思特 Spectrum AWG 卡均配备 高速 PCIe 接口,可实现每秒数十亿字节的数据传输,确保连续波形流的稳定供给。

为减轻 CPU 计算压力,系统还支持 SCAPP 选项,可利用 NVIDIA CUDA GPU 加速器 实现高效数据处理。

3.工作模式详解

在流式 FIFO 模式下,板上内存用作输入数据的 FIFO 缓冲区。这可以补偿用户应用程序暂时停滞导致的事件,从而使流式传输非常可靠。然而,缓冲区也会引入延迟,这在某些应用中可能不利,例如闭环反馈系统和通用控制系统。

为了更快地响应并减少数据传输,AWG 具有序列模式,其中可以以可配置的顺序循环不同的预存储序列,并且可以根据外部触发输入触发序列之间的切换。

然而,序列模式仍然使用一个小型 FIFO 缓冲区。因此,如果在外部输入上触发序列更改,则 FIFO缓冲区中的旧数据仍然需要传输到输出,并且由于 FIFO 缓冲区中旧数据的数量变化,它也可能导致特定模式和使用案例的动态行为中存在不确定性。

二、DDS模式

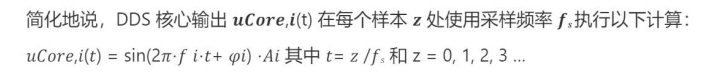

当应用仅需生成正弦信号时,可启用全新的 DDS 模式。该模式利用 FPGA 硬件直接在卡上实时生成连续正弦波,用户只需设置频率、幅度和初始相位即可。

1.什么是DDS?

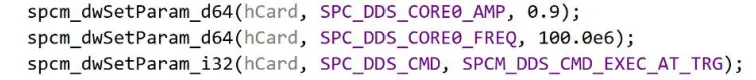

示例 1:如果您只想生成一个 100 MHz 和 90% 幅度(DAC 满量程范围的)连续正弦波,则只需使用 DDS 模式向卡发送 3 个特定命令:

2.DDS 模式有哪些优势?

✓ 计算任务下放至硬件:波形样本生成由 AWG 卡上的 FPGA 实时完成,大幅降低主机 CPU 负担。

✓ 极低的数据传输量:仅需发送“参数变更”指令(如频率跳变),无需传输完整波形数据,显著减少通信开销。

✓ 低延迟与高响应性:由于无需填充大型 FIFO 缓冲区,响应延迟更小,特别适合:

-

- 闭环反馈系统

-

- 实时控制系统

-

- 快速跳频应用

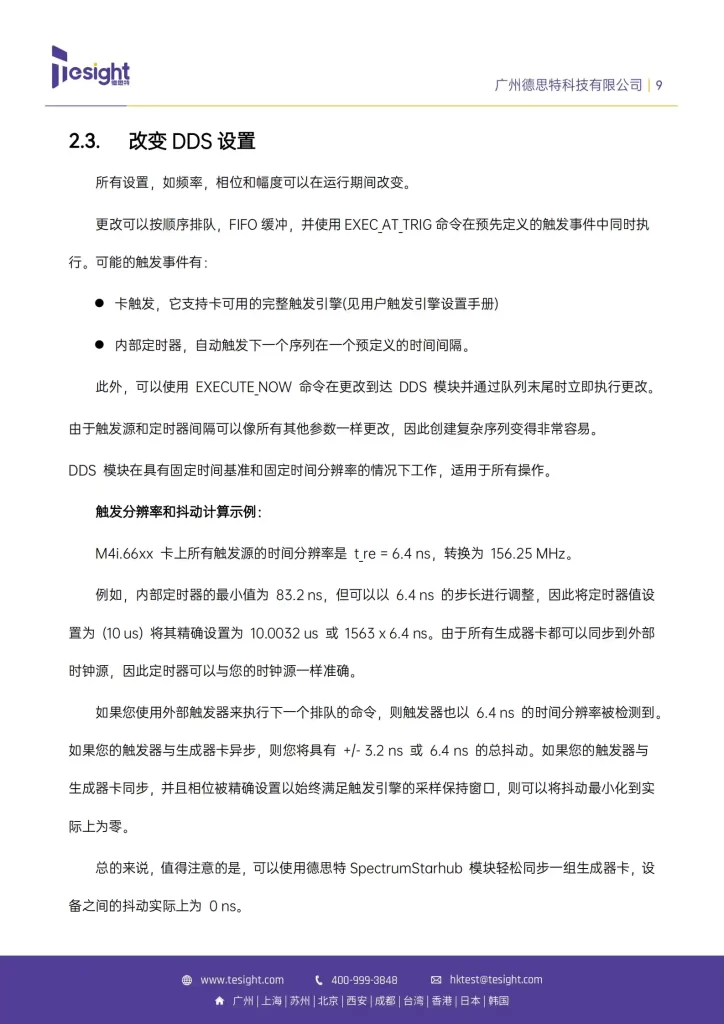

✓ 确定性响应与相位连续性

-

- 外部触发事件可实现确定性延迟响应

-

- 保证信号在跳变时相位连续,避免突变引起的干扰

✓ 编程简化

-

- 提供高级命令接口(如 set_frequency()、set_amplitude()),无需手动计算波形样本

-

- 降低开发复杂度,减少出错概率

3.DDS 模式有哪些劣势?

❌ 仅适用于周期性正弦信号

-

- 虽可近似其他波形(如方波、三角波),但精度有限

-

- 建议:若需复杂非正弦波形,仍应使用传统 AWG 模式

❌ 触发抖动较高

在 1.25 GS/s 采样率下:

-

- DDS 模式:触发到输出抖动 ≈ 6.6 ns

-

- 标准重放模式:抖动 ≈ 800 ps(即 0.8 ns,仅一个样本周期)

因此,DDS 的触发抖动约为标准模式的 8 倍。对于对触发时序精度要求极高的应用(如精密测量、同步系统),需权衡 DDS 的便利性与抖动性能。

三、总结

-

- 若需高精度、复杂波形 → 选用 AWG 模式

-

- 若需高效、连续正弦信号与快速动态响应 → 推荐使用 DDS 模式

- 相关产品

• 德思特板卡式AWG和DDS

- 快速16位DAC,带基于FPGA的DDS

- PCIe、PXIe或以太网可选,最多24个通道

- DDS频率DC至200MHz

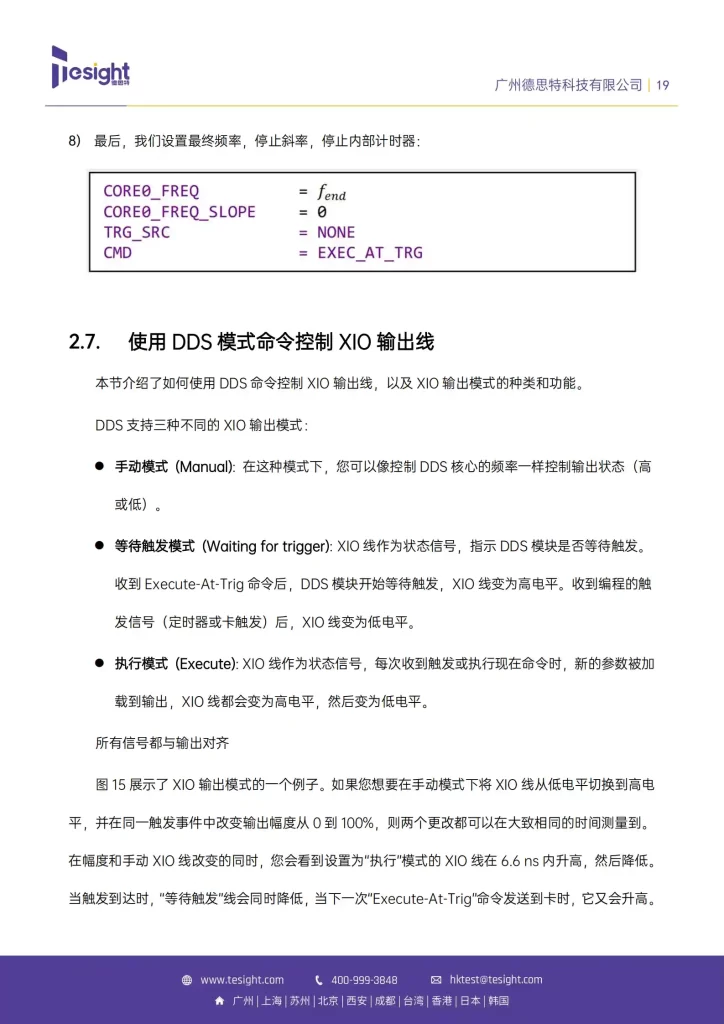

- DDS命令可以以6.4ns的间隔发出

- 固定触发到输出延迟

- 输出电平±80mV至±2.5V,50Ohm

- 本机DDS命令:频率、幅度、相位、频率斜率、幅度斜率、等待触发、数字输出

- 巨大的板载内存,每4个通道可容纳5.12亿个DDS命令

德思特AWG DDS模式应用白皮书

- 精准术语解释:DDS 与 AWG 模式核心技术对比全解析

-全流程参数配置:DDS 核心参数设置与行为控制详尽指导

-实例操作指导:量子操控、AOM/AOD 驱动与多音信号生成实战

- 底层编程接口详解:寄存器级调用与硬件控制流程图解