上期聚焦DAC输出特性,探讨了sinc衰减与补偿方案(数字滤波 vs. 模拟滤波)。信号链的完整性不仅在于“发送”,更在于精准“接收”。

本期,德思特将带您深入ADC芯片的“基本功”测试——静态参数。 我们将以斜坡测试(Ramp Test) 为核心,手把手详解其工程文件的配置要点,助您掌握评估ADC线性度(INL/DNL)等关键指标的实用方法。

一、确认测试适用性

在进行本测试之前,首先需要确认我们的待测 ADC 是否适用于斜坡测试。

1.适用场景

斜坡测试特别适用于中低速采样率且精度要求较高的 ADC。此测试旨在精确评估 ADC 的静态转换性能,涵盖的关键参数包括:

- 增益误差(Gain Error)

- 失调误差(Offset Error)

- 积分非线性(INL)

- 微分非线性(DNL)

- 总未调整误差(TUE)

2.核心原理

斜坡测试通过精密时钟控制系统调控测试时序,实现如下流程:

- 信号发生器(AWG)输出一个已知电压值

- ADC 对该电压进行转换

- 测试系统记录其数字输出

- 循环上述过程,使测试电压遍历整个 ADC 输入范围

优势:

- 每个 ADC 输出编码与 AWG 实际输出电压一一对应

- 建立映射关系后,可绘制出 ADC 的实际转换曲线

- 与理想曲线对比,直观、精确地计算各项关键性能参数

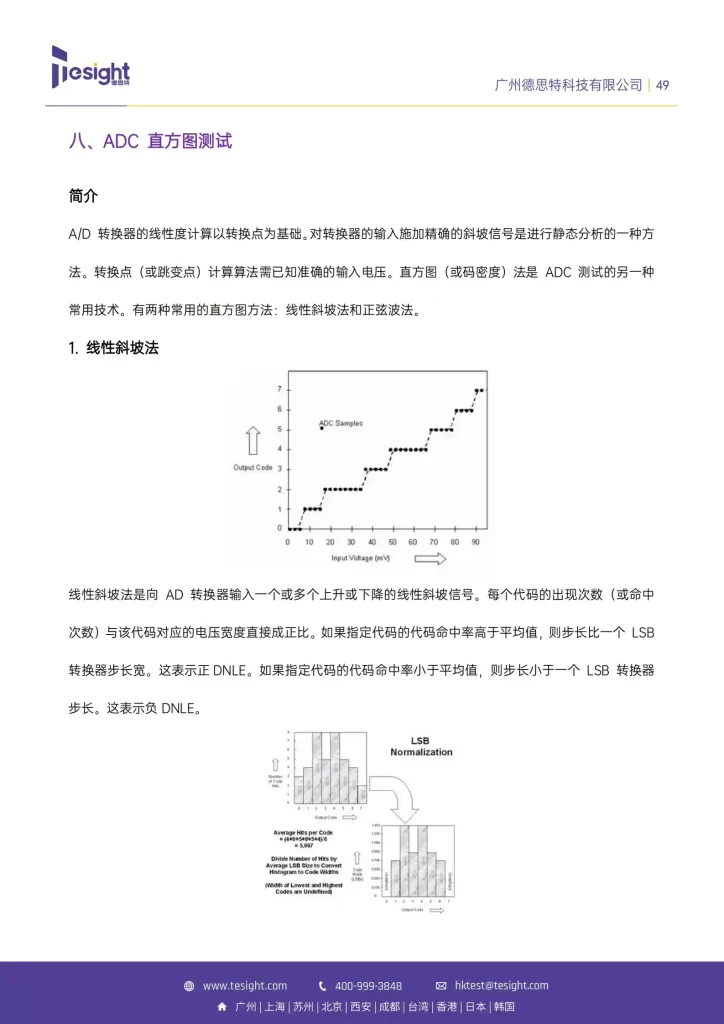

3.斜坡测试 vs 直方图测试

为帮助理解两种主流静态测试方法的区别,我们整理了以下对比表格:

4.为何选择斜坡测试?

尽管过去因控制复杂、计算量大而被部分工程师回避,但随着 德思特ADC/DAC测试系统的推出,这些问题已被解决:

- 所有控制步骤和算法高度集成

- 用户实现一键自动化操作

- 无需关注底层技术细节

- 提升测试效率,减少采样点数量

本文选择斜坡测试作为示例,正是为了展示 德思特ADC/DAC测试系统 如何简化复杂测试流程,提升工程效率。

二、硬件准备

“良好的开端是成功的一半。”

然而传统硬件准备过程繁琐、易错,涉及:

- 参数预估

- 仪器选型

- 控制软件编程调试

- 载板设计与制作

1.仪器部分准备

借助 德思特ADC/DAC测试系统,这一切变得异常简单:

- 用户只需根据待测 ADC 特点选择功能模块

- 专业团队负责整体交付

- 收到即为完整可用的测试系统

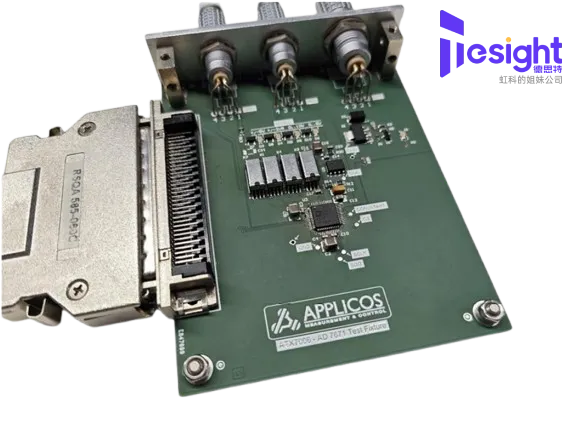

2.待测部分准备

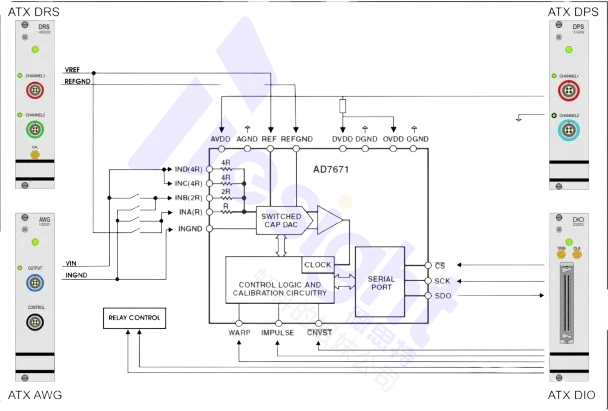

当仪器就绪后,工程师只需专注于测试芯片载板设计。得益于 德思特ADC/DAC测试系统集成:

- 数字 IO

- 供电电源

- 高精度参考电压源

载板设计已被极大简化,核心任务仅剩一项:

将待测芯片引脚连接至标准连接器,以便与系统线缆对接

完整原理图及相关资料,请联系德思特获取

系统扩展性设计亮点:

- 无需额外逻辑控制芯片驱动继电器

- ADC/DAC测试系统 DIO模块 原生提供 8 个静态数字输出通道

- 结合 MOS 管即可轻松驱动继电器

这些通道还可直接控制 UUT 的功能设置引脚,灵活切换工作状态

END

掌握ADC静态参数测试的核心——斜坡测试(Ramp Test)的硬件配置要点,是评估INL/DNL等关键性能指标的第一步。

本期我们手把手带您梳理了测试适用性判断与硬件配置的关键细节,为您搭建起精准测试的“地基”。

下期预告: 硬件就绪,软件赋能!下一期,我们将深入斜坡测试的软件配置实战,带您一步步解析工程文件的设置秘诀,让测试数据精准呈现。如何高效分析结果、优化流程?敬请锁定德思特测试测量!

行动建议: 请保存好本期配置要点,提前准备好您的测试环境,我们下期软件篇见!

- 相关产品

• 德思特ADC/DAC自动化测试系统

德思特ADC/DAC测试系统是一套9槽ATE芯片测试平台,模块化设计确保灵活性与扩展性,专注于数模及模数转换芯片的深度测试。系统囊括ADC/DAC全范围线性动态评估,搭载DIO时钟同步模块,可测8-24 bit ADC/DAC,以高达400 MHz的采样速率,重塑高效芯片测试新标准。

德思特ADC、DAC芯片测试白皮书

- 精准术语解释:20+关键ADC术语全解析,全面理解采样、抖动、非线性误差等影响性能的核心因素。

- 全流程参数计算:静态参数、动态分析、ENOB / SNR / SFDR / THD等核心指标计算方法详尽剖析。

- 实例操作指导:涵盖AD7671 / AD9244 / LTC2641等多种芯片真实测试配置与操作流程指导。